### COMPUTER ORGANIZATION AND ARCHITECTURE

# UNIT-1

# **Digital Logic Circuits and Digital Components**

The digital computer is a digital system that performs various computational tasks. The word digital implies that the information in the computer is represented by variables that take a limited number of discrete values. Digital computers use the binary number system, which has two digits: bit 0 and 1. A binary digit is called a bit. Information is represented in digital computers in groups of bits. By using various coding techniques, groups of bits can be made to represent not only binary numbers but also other discrete symbols, such as decimal digits or letters of the alphabets.

A computer system is sometimes subdivided into two functional entities: hardware and software. The hardware of the computer consists of all the electronic components and electromechanical devices that comprise the physical entity of the device. Computer software consists of the instructions and data that the computer manipulates to perform various data-processing tasks. A sequence of instructions for the computer is called a program. The data that are manipulated by the program constitute the data base.

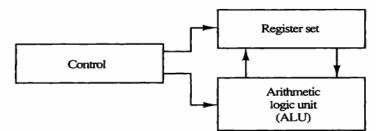

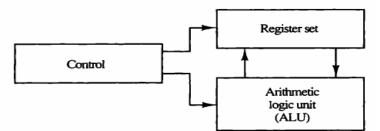

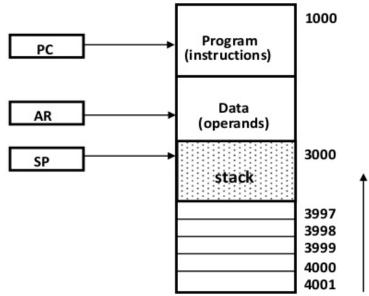

The hardware of the computer is usually divided into three major parts as shown below, central processing unit (CPU) contains an arithmetic and logic unit for manipulating data, a number of registers for storing data, and control circuits for fetching and executing instructions. The memory of a computer contains storage for instructions and data. It is called a random access memory (RAM) because the CPU can access any location in memory at random and retrieve the binary information within a fixed interval of time. The input and output processor (IOP) contains electronic circuits for communicating and controlling the transfer of information between the computer and the outside world. The input and output devices connected to the computer include keyboards, printers, terminals, magnetic disk drives, and other communication devices.

Fig. Block Diagram of Computer

### COMPUTER ORGANIZATION AND ARCHITECTURE

**Computer organization** is concerned with the way the hardware components operate and the way they are connected together to form the computer system. The various components are assumed to be in place and the task is to investigate the organizational structure to verify that the computer parts operate as intended.

**Computer design** is concerned with the hardware design of the computer. Once the computer specifications are formulated, it is the task of the designer to develop hardware for the system. Computer design is concerned with the determination of what hardware should be used and how the parts should be connected. This aspect of computer hardware is sometimes referred to as computer implementation.

**Computer architecture** is concerned with the structure and behavior of the computer as seen by the user. It includes the information formats, the instruction set, and techniques for addressing memory. The architectural design of a computer system is concerned with the specifications of the various functional modules, such as processors and memories, and structuring them together into a computer system.

### **1.1 Logic Gates**

Binary information is represented in digital computers by physical quantities called signals . Electrical signals such as voltages exist throughout the computer in either one of two recognizable states. The two states represent a binary variable that can be equal to 1 or 0. For example, a particular digital computer may employ a signal of 3 volts to represent binary 1 and 0.5 volt to represent binary 0. The input terminals of digital circuits accept binary signals of 3 and 0.5 volts and the circuits respond at the output terminals with signals of 3 and 0.5 volts to represent binary input and output corresponding to 1 and 0, respectively.

The manipulation of binary information is done by logic circuits called gates. Gates are blocks of hardware that produce signals of binary 1 or 0 when input logic requirements are satisfied. A variety of logic gates are commonly used in digital computer systems. Each gate has a distinct graphic symbol and its operation can be described by means of an algebraic expression. The input-output relationship of the binary variables for each gate can be represented in tabular form by a truth table.

### COMPUTER ORGANIZATION AND ARCHITECTURE

| Name                               | Graphic<br>symbol | Algebraic<br>function             | Trut h<br>table                                                                                          |

|------------------------------------|-------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------|

| AND                                |                   | $F = x \cdot y$                   | x y F<br>0 0 0<br>0 1 0<br>1 0 0<br>1 1 1                                                                |

| OR                                 |                   | F = x + y                         | $\begin{array}{c ccc} x & y & F \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \end{array}$  |

| Inverter                           | xF                | $F = x^{\prime}$                  | x F<br>0 1<br>1 0                                                                                        |

| Buffer                             | xF                | F = x                             | x F<br>0 0<br>1 1                                                                                        |

| NAND                               |                   | F = (xy)'                         | $\begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 1 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \end{array}$ |

| NOR                                |                   | F = (x + y)'                      | $\begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 0 \end{array}$ |

| Exclusive-OR<br>(XOR)              |                   | $F = xy' + x'y$ $= x \oplus y$    | $\begin{array}{cccc} x & y & F \\ 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \end{array}$          |

| Exclusive-NOR<br>or<br>equivalence |                   | $F = xy + x'y'$ $= (x \oplus y)'$ | x y F<br>0 0 1<br>0 1 0<br>1 0 0<br>1 1 1                                                                |

### COMPUTER ORGANIZATION AND ARCHITECTURE

### **1.2 Boolean Algebra**

Boolean algebra is an algebra that deals with binary variables and logic operations. The variables are designated by letters such as A, B, x, andy. The three basic logic operations are AND, OR, and complement. A Boolean function can be expressed algebraically with binary variables, the logic operation symbols, parentheses, and equal sign. For a given value of the variables, the Boolean function can be either 1 or 0. Consider, for example, the Boolean function

$\mathbf{F} = \mathbf{x} + \mathbf{y'z}$

The function F is equal to 1 if x is 1 or if both y' and z are equal to I; F is equal to 0 otherwise. But saying that y' = 1 is equivalent to saying that y = 0 since y' is the complement of y. Therefore, we may say that F is equal to 1 if x = 1 or if yz = 01. The relationship between a function and its binary variables can be represented in a truth table. To represent a function in a truth table we need a list of the 2' combinations of then binary variables.

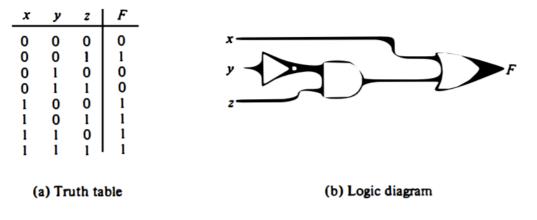

In the following fig (a) there are eight possible distinct combinations for assigning bits to the three variables x, y, and z. The function F is equal to 1 for those combinations where x = 1 or yz = 01; it is equal to 0 for all other combinations.

A Boolean function can be transformed from an algebraic expression into a logic diagram composed of AND, OR, and inverter gates. The logic diagram for F is shown in Fig. (b). There is an inverter for input y to generate its complement y'. There is an AND gate for the term y'z, and an OR gate is used to combine the two terms. In a logic diagram, the variables of the function are taken to be the inputs of the circuit, and the variable symbol of the function is taken as the output of the circuit. The purpose of Boolean algebra is to facilitate the analysis and design of digital circuits. It provides a convenient tool to:

- 1. Express in algebraic form a truth table relationship between binary variables.

- 2. Express in algebraic form the input-output relationship of logic diagrams.

- 3. Find simpler circuits for the same function.

A Boolean function specified by a truth table can be expressed algebraically in many different ways. By manipulating a Boolean expression according to Boolean algebra rules, one may

## COMPUTER ORGANIZATION AND ARCHITECTURE

obtain a simpler expression that will require fewer gates. To see how this is done, we must first study the manipulative capabilities of Boolean algebra.

### 1.2.1 Rule in Boolean Algebra

Following are the important rules used in Boolean algebra.

- Variable used can have only two values. Binary 1 for HIGH and Binary 0 for LOW.

- Complement of a variable is represented by an overbar. Thus, complement of variable B is represented as B. Thus if B = 0 then B=1 and B = 1 then B= 0.

- OR-ing of the variables is represented by a plus (+) sign between them. For example OR-ing of A, B, C is represented as A + B + C.

- Logical AND-ing of the two or more variable is represented by writing a dot between them such as A.B.C. Sometimes the dot may be omitted like ABC.

### 1.2.2 Laws of Boolean Algebra

Boolean Algebra Laws are used to simplify boolean expressions.

#### **Basic Boolean Algebra Laws**

1. Idempotent Law

•

$$A * A = A$$

•

$$A + A = A$$

- 2. Associative Law

- (A \* B) \* C = A \* (B \* C)

- (A + B) + C = A + (B + C)

- 3. Commutative Law

- A \* B = B \* A

- $\bullet \quad A+B=B+A$

- 4. Distributive Law

- A \* (B + C) = A \* B + A \* C

- A + (B \* C) = (A + B) \* (A + C)

- 5. Identity Law

- A \* 0 = 0 A \* 1 = A

- A + 1 = 1 A + 0 = A

- 6. Complement Law

- $A * \sim A = 0$

- $A + \sim A = 1$

COMPUTER ORGANIZATION AND ARCHITECTURE

7. Involution Law

•

$$\sim (\sim A) = A$$

8. DeMorgan's Law

•

$$\sim (A * B) = \sim A + \sim B$$

•  $\sim (A + B) = \sim A * \sim B$

**Redundancy Laws**

9. Absorption

•

$$A + (A * B) = A$$

•

$$A * (A + B) = A$$

10.

•

$$(A * B) + (A * ~B) = A$$

•

$$(A + B) * (A + \sim B) = A$$

11.

•

$$A + (\sim A * B) = A + B$$

•

$$A * (\sim A + B) = A * B$$

The purpose of Boolean algebra is to analysis and design of digital circuits, it provides a convenient tool to

A Boolean function specified by a truth table can be expressed algebraically in many different ways. By manipulating a Boolean expression according to Boolean algebra rules, one may obtain a simpler expression that will require fewer gates. To see how this is done, we must first study the manipulative capabilities of Boolean algebra.

### **1.2.3 DeMorgan's theorem**

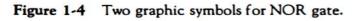

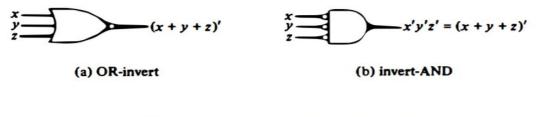

DeMorgan's theorem is very important in dealing with NOR and NAND gates. It states that a NOR gate that performs the (x + y)' function is equivalent to the function x'y'. Similarly, a NAND function can be expressed by either (xy)' or (x' + y'). For this reason the NOR and NAND gates have two distinct graphic symbols, as shown in Figs. 1-4 and 1-5. Instead of representing a NOR gate with an OR graphic symbol followed by a circle, we can represent it by an AND graphic symbol preceded by circles in all inputs. The invert-AND symbol for the NOR gate follows from DeMorgan's theorem and from the convention that small circles denote complementation. Similarly, the NAND gate has two distinct symbols, as shown in Fig. 1-5.

COMPUTER ORGANIZATION AND ARCHITECTURE

Figure 1-5 Two graphic symbols for NAND gate.

### **1.2.4** Complement of a Function F

The complement of a function F when expressed in a truth table is obtained by interchanging I's and D's in the values of F in the truth table. When the function is expressed in algebraic form, the complement of the function can be derived by means of DeMorgan's theorem. The general form of DeMorgan's theorem can be expressed as follows:

$$(X1+X2+X3+\cdots+Xn)' = X1' X2' X3'\cdots Xn'$$

$(X1 X2X3\cdots Xn)' = X1'+X2' + X3'+\cdots + Xn'$

As an example, consider the following expression and its complement:

F = AB + C'D' + B'D F' = (A' + B')(C + D)(B + D')

### **1.3 Map Simplification**

The complexity of the logic diagram that implements a Boolean function is related directly to the complexity of the algebraic expression from which the function is implemented. The truth table representation of a function is unique, but the function can appear in many different forms when expressed algebraically. The expression may be simplified using the basic relations of Boolean algebra. However, this procedure is sometimes difficult because it lacks specific rules for predicting each succeeding step in the manipulative process. The map method provides a simple, straightforward procedure for simplifying Boolean expressions. This method may be regarded as a pictorial arrangement of the truth table which allows an easy interpretation for choosing the minimum number of terms needed to express the function algebraically. The map method is also known as the **Karnaugh-Map or K-Map**.

Each combination of the variables in a truth table is called a minterm. When expressed in a truth table a function of n variables will have 2" minterms, equivalent to the 2" binary numbers obtained from n bits. A Boolean function is equal to 1 for some minterms and to 0 for others. The

### COMPUTER ORGANIZATION AND ARCHITECTURE

information contained in a truth table may be expressed in compact form by listing the decimal equivalent of those minterms that produce a 1 for the function.

For example the below truth table can be expressed as

$F(x, y, z) = \sum (1, 4, 5, 6, 7)$

| x | У | z | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

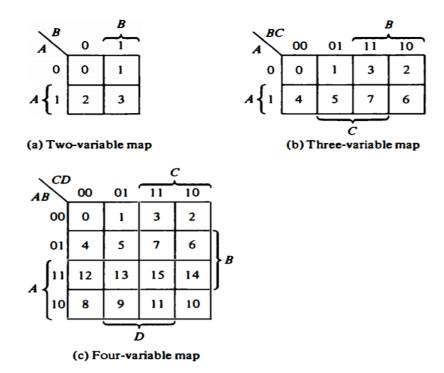

The maps for functions of two, three, and four variables are shown in Fig. 1-7. The number of squares in a map of n variables is 2". The 2" minterms are listed by an equivalent decimal number for easy reference. The minterm numbers are assigned in an orderly arrangement such that adjacent squares represent minterms that differ by only one variable. The variable names are listed across both sides of the diagonal line in the corner of the map. The O's and 1' s marked along each row and each column designate the value of the variables.

### COMPUTER ORGANIZATION AND ARCHITECTURE

### 1.3.1 Sum-of-products form

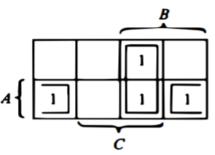

A Boolean function represented by a truth table is plotted into the map by inserting 1's in those squares where the function is I. The squares containing 1's are combined in groups of adjacent squares. These groups must contain a number of squares that is an integral power of 2. Groups of combined adjacent squares may share one or more squares with one or more groups. Each group of squares represents an algebraic term, and the OR of those terms gives the simplified algebraic expression for the function. The following examples show the use of the map for simplifying Boolean functions. In the first example we will simplify the Boolean function

$$F(A, B, C) = \sum (3, 4, 6, 7)$$

The simplified algebraic expression for the function is the OR of the two terms: F = BC + AC' four-variable map.  $F(A, B, C, D) = \sum (0, 1, 2, 6, 8, 9, 10)$

the simplified function is : F = B 'D' + B 'C' + A'CD'

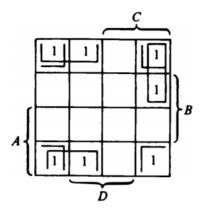

### **1.3.2 Product of Sums Simplification**

If the squares marked with 0's are combined, as shown in the diagram, we obtain the simplified complemented function: F' = AB + CD + BD' Taking the complement of F', we obtain the simplified function in product-of sums form: F = (A' + B')(C' + D')(B' + D)

COMPUTER ORGANIZATION AND ARCHITECTURE

Map for  $F(A, B, C, D) = \Sigma (0, 1, 2, 5, 8, 9, 10).$

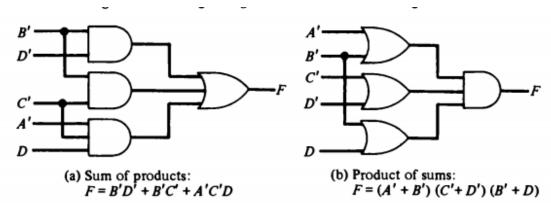

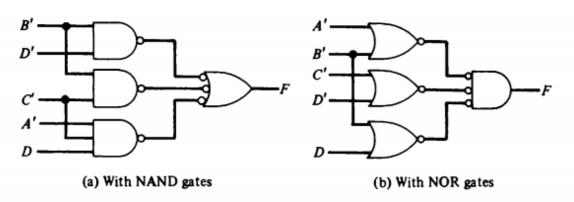

The Logic diagram for the **Sum-of-Products** and **Product-of-Sums** is shown in the following diagram.

Logic diagram using NAND and NOR gates are

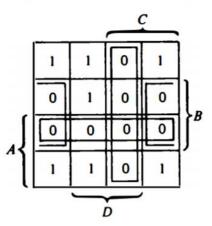

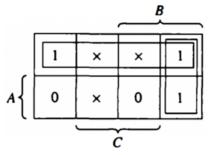

### 1.3.3 Don't-Care Conditions

The 1's and 0's in the map represent the min terms that make the function equal to 1 or 0. There are occasions when it does not matter if the function produces 0 or 1 for a given minterm. Since the

### COMPUTER ORGANIZATION AND ARCHITECTURE

function may be either 0 or 1, we say that we don't care what the function output is to be for this min term. Min terms that may produce either 0 or 1 for the function are said to be don't-care conditions and are marked with an x in the map. These don't-care conditions can be used to provide further simplification of the algebraic expression.

As an example, consider the following Boolean function together with the don't-care minterms:

$F(A, B, C) = \sum (0, 2, 6)$

$d(A, B, C) = \sum (1, 3, 5)$

The simplified expression is F = A' + BC'

### **1.4 Combinational Circuits**

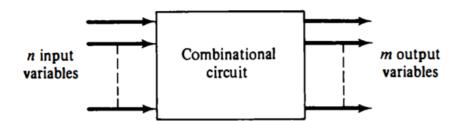

A combinational circuit is a connected arrangement of logic gates with a set of inputs and outputs. At any given time, the binary values of the outputs are a function of the binary combination of the inputs. A block diagram of a combinational circuit is shown in the following Figure. The n binary input variables come from an external source, the m binary output variables go to an external destination, and in between there is an interconnection of logic gates.

A combinational circuit can be described by a truth table showing the binary relationship between the n input variables and the m output variables. The truth table lists the corresponding output binary values for each of the 2" input combinations. A combinational circuit can also be specified with m Boolean functions, one for each output variable. Each output function is expressed in terms of the n input variables.

The design of combinational circuits starts from the verbal outline of the problem and ends in a logic circuit diagram. The procedure involves the following steps:

### **COMPUTER ORGANIZATION AND ARCHITECTURE**

- 1. The problem is stated.

- 2. The input and output variables are assigned letter symbols.

- 3. The truth table that defines the relationship between inputs and outputs is derived.

- 4. The simplified Boolean functions for each output are obtained.

- 5. The logic diagram is drawn.

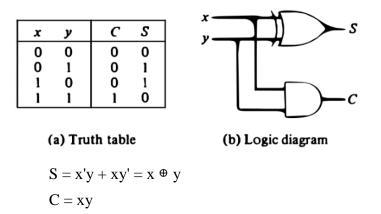

### 1.4.1 Half-Adder

The most basic digital arithmetic circuit is the addition of two binary digits. A combinational circuit that performs the arithmetic addition of two bits is called a half-adder. One that performs the addition of three bits (two significant bits and a previous carry) is called a full-adder. The name of the former stems from the fact that two half-adders are needed to implement a full-adder. The input variables of a half-adder are called the augend and addend bits. The output variables the sum and carry. It is necessary to specify two output variables because the sum of 1 + 1 is binary 10, which has two digits. We assign symbols x and y to the two input variables, and S (for sum) and C (for carry) to the two output variables. The truth table for the half-adder is shown in Fig. 1-16(a). The C output is 0 unless both inputs are I. The S output represents the least significant bit of the sum. The Boolean functions for the two outputs can be obtained directly from the truth table:

The logic diagram is shown in Fig. 1-16(b). It consists of an exclusive-OR gate and an AND gate.

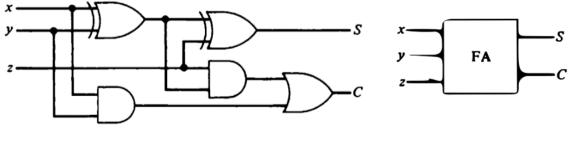

### 1.4.2 Full-Adder

A full-adder is a combinational circuit that forms the arithmetic sum of three input bits. It consists of three inputs and two outputs. Two of the input variables, denoted by x and y, represent the two significant bits to be added. The third input, z, represents the carry from the previous lower significant position. Two outputs are necessary because the arithmetic sum of three binary digits ranges in value from 0 to 3, and binary 2 or 3 needs two digits. The two outputs are designated by the symbols S (for sum) and C (for carry). The binary variable S gives the value of the least significant bit of the sum. The binary variable C gives the output carry. The truth table of the full-adder is shown in the following Table.

### **COMPUTER ORGANIZATION AND ARCHITECTURE**

| Ir | nputs |   | Out | puts |

|----|-------|---|-----|------|

| x  | у     | z | С   | S    |

| 0  | 0     | 0 | 0   | 0    |

| 0  | 0     | 1 | 0   | 1    |

| 0  | 1     | 0 | 0   | 1    |

| 0  | 1     | 1 | 1   | 0    |

| 1  | 0     | 0 | 0   | 1    |

| 1  | 0     | 1 | 1   | 0    |

| 1  | 1     | 0 | 1   | 0    |

| 1  | 1     | 1 | 1   | 1    |

The eight rows under the input variables designate all possible combinations that the binary variables may have. The value of the output variables are determined from the arithmetic sum of the input bits. When all input bits are 0, the output is 0. The S output is equal to 1 when only one input is equal to 1 or when all three inputs are equal to I. The C output has a carry of 1 if two or three inputs are equal to I.

(a) Logic diagram

(b) Block diagram

The logic diagram of the full-adder is drawn in the above figure. Note that the fulladder circuit consists of two half-adders and an OR gate. Realizing that  $x'y + xy' = xa_1y$  and including the expression for output S, we obtain the two Boolean expressions for the full-adder:

# $S=x\oplus y\oplus z$ $C = xy + (x\oplus y)z$

### **1.5 Flip-Flops**

The digital circuits considered thus far have been combinational, where the outputs at any given time are entirely dependent on the inputs that are present at that time. Although every digital system is likely to have a combinational circuit, most systems encountered in practice also include storage elements, which require that the system be described in terms of sequential circuits. The most common type of sequential circuit is the synchronous type.

Synchronization is achieved by a timing device called a clock pulse generator that produces a periodic train of clock pulses. The storage elements employed in clocked sequential circuits are called flip-flops. A flip-flop is a binary cell capable of storing one bit of information. It has two

### COMPUTER ORGANIZATION AND ARCHITECTURE

outputs, one for the normal value and one for the complement value of the bit stored in it. A flip-flop maintains a binary state until directed by a clock pulse to switch states. The difference among various types of flip-flops is in the number of inputs they possess and in the manner in which the inputs affect the binary state. The most common types of flip-flops are presented below.

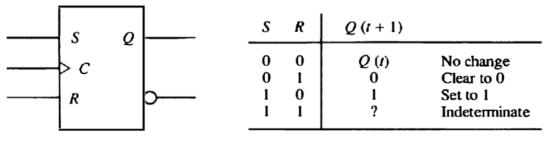

### 1.5.1. SR Flip-Flop

The graphic symbol of the SR flip-flop is shown in Figure. It has three inputs, labelled S (for set), R (for reset), and C (for clock). It has an output Q and sometimes the flip-flop has a complemented output, which is indicated with a small circle at the other output terminal. There is an arrowhead-shaped symbol in front of the letter C to designate a dynamic input. The dynamic indicator symbol denotes the fact that the flip-flop responds to a positive transition (from 0 to 1) of the input clock signal.

(a) Graphic symbol

The operation of the SR flip-flop is as follows. If there is no signal at the clock input C, the output of the circuit cannot change irrespective of the values at inputs S and R. Only when the clock signal changes from 0 to 1 can the output be affected according to the values in inputs S and R. If S = 1 and R = 0 when C changes from 0 to 1, output Q is set to 1. If S = 0 and R = 1 when C changes from 0 to 1, output Q is set to 1. If S = 0 and R = 1 when C changes from 0 to 1, output Q is cleared to 0. If both S and R are 0 during the clock transition, the output does not change. When both 5 and R are equal to 1, the output is unpredictable and may go to either 0 or 1, depending on internal timing delays that occur within the circuit.

The characteristic table shown above summarizes the operation of the SR flip-flop in tabular formThe S and R columns give the binary values of the two inputs. Q(t) is the binary state of the Q output at a given time (referred to as present state). Q(t + 1) is the binary state of the Q output after the occurrence of a clock transition (referred to as next state).

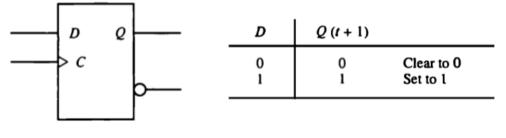

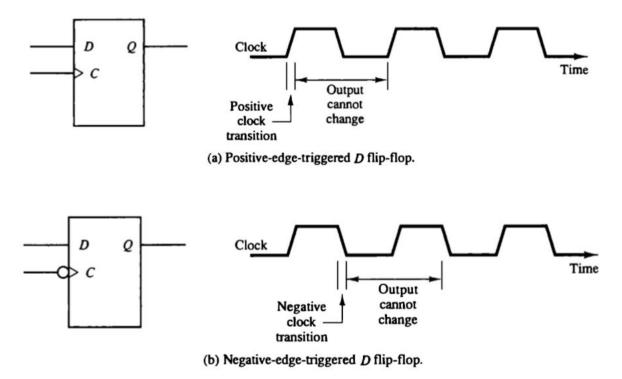

### 1.5.2. D Flip-Flop

The D (data) flip-flop is a slight modification of the SR flip-flop. An SR flip-flop is converted to a D flip-flop by inserting an inverter between S and R and assigning the symbol D to the single input. The D input is sampled during the occurrence of a clock transition from 0 to 1. If D = 1, the output of the flip-flop goes to the 1 state, but if D = 0, the output of the flip-flop goes to the 0 state. The graphic symbol and characteristic table of the D flip-flop are shown in Fig. 1-20. From the

<sup>(</sup>b) Characteristic table

### COMPUTER ORGANIZATION AND ARCHITECTURE

characteristic table we note that the next state Q(t + 1) is determined from the D input. The relationship can be expressed by a characteristic equation: Q(t + 1) = D

Although a D flip-flop has the advantage of having only one input (excluding C), it has the disadvantage that its characteristic table does not have a "no change" condition Q(t + 1) = Q(t). The "no change" condition can be accomplished either by disabling the clock signal or by feeding the output back into the input, so that clock pulses keep the state of the flip-flop unchanged.

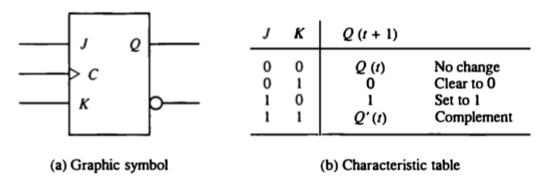

### 1.5.3 JK-Flip-Flop

A JK flip-flop is a refinement of the SR flip-flop in that the indeterminate condition of the SR type is defined in the JK type. Inputs J and K behave like inputs S and R to set and clear the flip-flop, respectively. When inputs J and K are both equal to 1, a clock transition switches the outputs of the flip-flop to their complement state. The graphic symbol and characteristic table of the JK flip-flop are shown in following figure. The J input is equivalent to the S (set) input of the SR flip-flop, and the K input is equivalent to the R (clear) input. Instead of the indeterminate condition, the JK flip-flop has a complement condition Q(t + 1) = Q'(t) when both J and K are equal to 1.

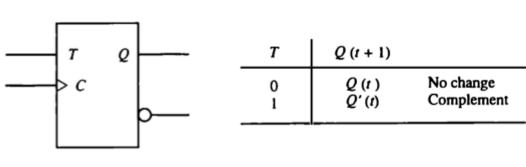

### 1.5.4 T-Flip-Flop

Another type of flip-flop found in textbooks is the T (toggle) flip-flop. This flip-flop, shown in Fig. 1-22, is obtained from a JK type when inputs J and K are connected to provide a single input designated by T. The T flip-floptherefore has only two conditions. When T = 0 (J = K = 0) a clock transition does not change the state of the flip-flop. When T = 1 (J = K = 1) a clock transition complements the state of the flip-flop. These conditions can be expressed by a characteristic equation:

### COMPUTER ORGANIZATION AND ARCHITECTURE

(a) Graphic symbol

(b) Characteristic table

### 1.5.5 Edge-Triggered Flip-Flops

$Q(t+1) = Q(t) \oplus T$

The most common type of flip-flop used to synchronize the state change during a clock pulse transition is the edge-triggered flip-flop. In this type of flip-flop, output transitions occur at a specific level of the clock pulse. When the pulse input level exceeds this threshold level, the inputs are locked out so that the flip-flop is unresponsive to further changes in inputs until the clock pulse returns to 0 and another pulse occurs. Some edge-triggered flip-flops cause a transition on the rising edge of the clock signal (positive-edge transition), and others cause a transition on the falling edge (negative-edge transition).

### COMPUTER ORGANIZATION AND ARCHITECTURE

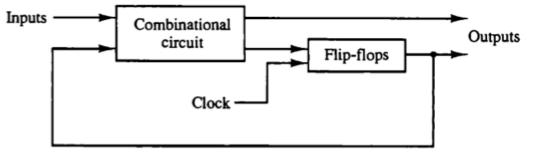

# **1.6 Sequential Circuits**

A sequential circuit is an interconnection of flip-flops and gates. The gates by themselves constitute a combinational circuit, but when included with the flip-flops, the overall circuit is classified as a sequential circuit. The block diagram of a clocked sequential circuit is shown in following figure. It consists of a combinational circuit and a number of clocked flip-flops. In general, any number or type of flip-flops may be included. As shown in the diagram,

The combinational circuit block receives binary signals from external inputs and from the outputs of flip-flops. The outputs of the combinational circuit go to external outputs and to inputs of flip-flops. The gates in the combinational circuit determine the binary value to be stored in the flip-flops after each clock transition. The outputs of flip-flops, in turn, are applied to the combinational circuit inputs and determine the circuit's behavior. This process demonstrates that the external outputs of a sequential circuit are functions of both external inputs and the present state of the flip-flops. Moreover, the next state of flip-flops is also a function of their present state and external inputs. Thus a sequential circuit is specified by a time sequence of external inputs, external outputs, and internal flip-flop binary states.

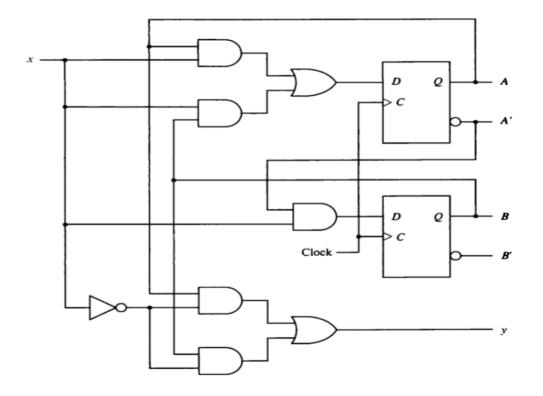

An example of a sequential circuit is shown in Figure

COMPUTER ORGANIZATION AND ARCHITECTURE

# **DIGITAL COMPONENTS**

### **1.7 Integrated Circuits**

Digital circuits are constructed with integrated circuits. An integrated circuit (abbreviated IC) is a small silicon semiconductor crystal called chip containing the electronic components for the digital gates. The various gates are in interconnected inside the chip to form the required circuit. The chip is mounted on a ceramic or plastic container, and connections are welded by thin gold wines to external pins to form the integrated circuit. The number of pins may range from 14 in a small IC package to 100 or more in a larger package. Each IC has a numeric designation printed on the surface of the package for identification.

As the technology of ICs has improved, the number of gates that can be put in a single chip has increased considerably.

**Small-Scale integration (SSI)** devices contain several independent gates in a single package. The inputs and outputs of the gates are connected directly to the pins in the package. The number of gates is usually less than 10 and is limited by the number of pins available in the IC.

**Medium-scale integration (MSI)** devices have a complexity of approximately 10 to 200 gates in a single package. They usually perform specific elementary digital functions such as decoders, adders, and registers.

### COMPUTER ORGANIZATION AND ARCHITECTURE

**Large-scale integration** (**LSI**) devices contain between 200 and a few thousand gates in a single package. They include digital systems, such as processors, memory chips, and programmable modules. **Very-large-scale integration** (**VLSI**) devices contain thousands of gates within a single package. Examples are large memory arrays and complex microcomputer chips. Because of their small size and low cost, VLSI devices have revolutionized the computer system design technology, giving designers the capability to create structures that previously were not economical.

Digital integrated circuits are classified not only by their logic operation but also by digital logic family. Each logic family has its own basic electronic circuit upon which more complex digital circuits and functions are developed. The basic circuit in each technology is either a NAND, a NOR, or an inverter gate. Many different logic families of integrated circuits have been introduced commercially. The following are the most popular.

- TTL- Transistor-transistor logic

- ECL Emitter-coupled logic

- MOS Metal-oxide semiconductor

- CMOS Complementary metal-oxide semiconductor

The **transistor-transistor logic** family was an evolution of a previous technology that used diodes and transistors for the basic NAND gate. This technology was called DTL, for "diode-transistor logic." Later the diodes were replaced by transistors to improve the circuit operation and the name of the logic family was changed to "transistor-transistor logic." This is the reason for mentioning the word "transistor" twice.

The **emitter-coupled logic** (ECL) family provides the highest-speed digital circuits in integrated form. ECL is used in systems such as supercomputers and signal processors where high speed is essential

The **metal-oxide semiconductor** (MOS) is a unipolar transistor that depends on the flow of only one type of carrier, which may be electrons (n-channel) or holes (p-channel). This is in contrast to the bipolar transistor used in TIL and ECL gates, where both carriers exist during normal operation.

The **complementary MOS** (CMOS) technology uses PMOS and NMOS transistors connected in a complementary fashion in all circuits. The most important advantages of CMOS over bipolar are the high packing density of circuits, a simpler processing technique during fabrication, and a more economical operation because of low power consumption.

# **1.8 Decoders**

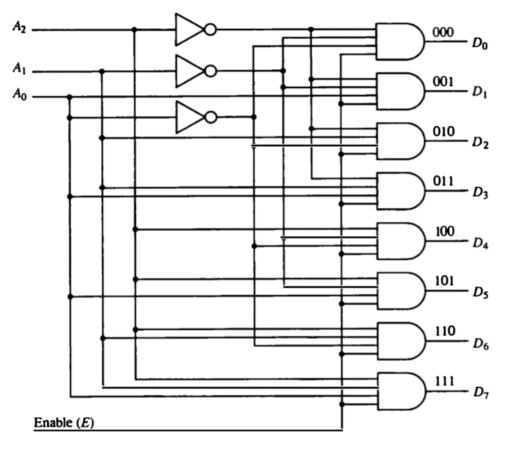

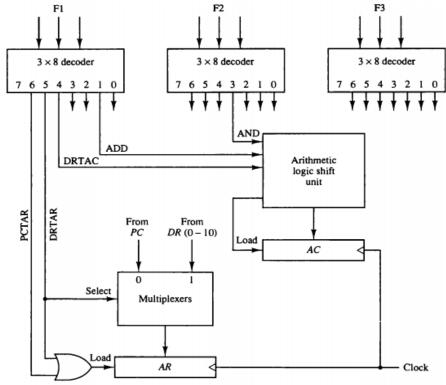

Discrete quantities of information are represented in digital computers with binary codes. A binary code of n bits is capable of representing up to  $2^n$  distinct elements of the coded information. A decoder is a combinational circuit that converts binary information from the n coded inputs to a maximum of  $2^n$  unique outputs. If the n-bit coded information has unused bit combinations, the decoder may have less than  $2^n$  outputs. The decoders presented in this section are called n-to-m-line decoders, where m <= $2^n$ . Their purpose is to generate the  $2^n$  (or fewer) binary combinations of the n input variables. A decoder has n inputs and m outputs and is also referred to as an n x m decoder. The logic diagram of a 3-to-8-line decoder is shown in Figure.

COMPUTER ORGANIZATION AND ARCHITECTURE

The three data inputs,  $A_0$ ,  $A_1$ , and  $A_n$  are decoded into eight outputs, each outputrepresenting one of the combinations of the three binary input variables. The three inverters provide the complement of the inputs, and each of the eight AND gates generates one of the binary combination. A particular application of this decoder is a binary-to-octal conversion. The input variables represent a binary number and the outputs represent the eight digits of the octal number system. However, a 3to-8-line decoder can be used for decoding any 3-bit code to provide eight outputs, one for each combination of the binary code.

Commercial decoders include one or more enable inputs to control the operation of the circuit. The decoder of the above Figure has one enable input, E. The decoder is enabled when E is equal to 1 and disabled when E is equal to 0. The operation of the decoder can be clarified using the truth table listed in the following Table. When the enable input E is equal to 0, all the outputs are equal to 0 regardless of the values of the other three data inputs. The three x's in the table designate don't-care conditions. When the enable input is equal to 1, the decoder operates in a normal fashion. For each possible input combination, there are seven outputs that are equal to 0 and only one that is equal to 1. The output variable whose value is equal to 1 represents the octal number equivalent of the binary number that is available in the input data lines.

| Enable |       | Inputs                |                |    |                |    | Out | puts |                |       |    |

|--------|-------|-----------------------|----------------|----|----------------|----|-----|------|----------------|-------|----|

| E      | $A_2$ | <i>A</i> <sub>1</sub> | A <sub>0</sub> | D7 | D <sub>6</sub> | D5 | D4  | D3   | D <sub>2</sub> | $D_1$ | Do |

| 0      | ×     | ×                     | ×              | 0  | 0              | 0  | 0   | 0    | 0              | 0     | 0  |

| 1      | 0     | 0                     | 0              | 0  | 0              | 0  | 0   | 0    | 0              | 0     | 1  |

| 1      | 0     | 0                     | 1              | 0  | 0              | 0  | 0   | 0    | 0              | 1     | 0  |

| 1      | 0     | 1                     | 0              | 0  | 0              | 0  | 0   | 0    | 1              | 0     | 0  |

| 1      | 0     | 1                     | 1              | 0  | 0              | 0  | 0   | 1    | 0              | 0     | 0  |

| 1      | 1     | 0                     | 0              | 0  | 0              | 0  | 1   | 0    | 0              | 0     | 0  |

| 1      | 1     | 0                     | 1              | 0  | 0              | 1  | 0   | 0    | 0              | 0     | 0  |

| 1      | 1     | 1                     | 0              | 0  | 1              | 0  | 0   | 0    | 0              | 0     | 0  |

| 1      | 1     | 1                     | 1              | 1  | 0              | 0  | 0   | 0    | 0              | 0     | 0  |

### **COMPUTER ORGANIZATION AND ARCHITECTURE**

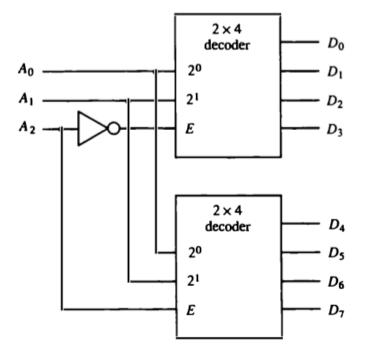

### **1.8.1 Decoder Expansion**

There are occasions when a certain-size decoder is needed but only smaller sizes are available. When this occurs it is possible to combine two or more decoders with enable inputs to form a larger decoder. Thus if a 6-to-64-line decoder is needed, it is possible to construct it with four 4-to-16-line decoders. The following figure shows how decoders with enable inputs can be connected to form a larger decoder. Two 2-to-4-line decoders are combined to achieve a 3-to-8-line decoder. The two least significant bits of the input are connected to both decoders. The most significant bit is connected to the enable input of one decoder and through an inverter to the enable input of the other decoder. It is assumed that each decoder is enabled when its E input is equal to 1. When E is equal to 0, the decoder is disabled and all its outputs are in the Olevel. When  $A_{1} = 0$ , the upper decoder is enabled and the lower is disabled. The lower decoder outputs become inactive with all outputs at 0. The outputs of the upper decoder generate outputs Do through D3, depending on the values of A1 and A0 (while  $A_{1} = 0$ ). When  $A_{2} = 1$ , the lower decoder is enabled and the upper is disabled. The lower decoder output generates the binary equivalent D4 through D, since these binary numbers have a 1 in the A, position. The example demonstrates the usefulness of the enable input in decoders or any other combinational logic component. Enable inputs are a convenient feature for interconnecting two or more circuits for the purpose of expanding the digital component into a similar function but with more inputs and outputs.

### **COMPUTER ORGANIZATION AND ARCHITECTURE**

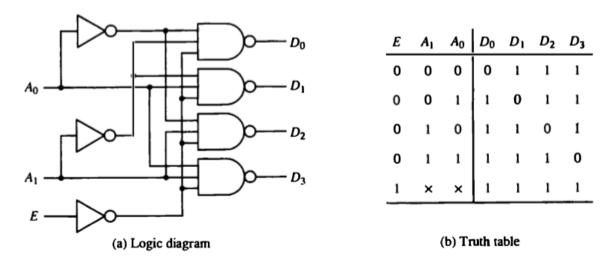

### 1.8.2 NAND Gate Decoder

Some decoders are constructed with NAND instead of AND gates. Since a NAND gate produces the AND operation with an inverted output, it becomes more economical to generate the decoder outputs in their complement form. A 2-to-4-line decoder with an enable input constructed with NAND gates is shown in Figure. The circuit operates with complemented outputs and a complemented enable input E. The decoder is enabled when E is equal to 0. As indicated by the truth table, only one output is equal to 0 at any given time; the other three outputs are equal to 1. The output whose value is equal to 0 represents the equivalent binary number in inputs A1 and A,. The circuit is disabled when E is equal to 1, regardless of the values of the other two inputs.

### COMPUTER ORGANIZATION AND ARCHITECTURE

When the circuit is disabled, none of the outputs are selected and all outputs are equal to 1. In general, a decoder may operate with complemented or uncomplemented outputs. The enable input may be activated with a 0 or with a 1 signal level.

### **1.9 Encoders**

An encoder is a digital circuit that performs the inverse operation of a decoder. An encoder has 2" (or less) input lines and n output lines. The output lines generate the binary code corresponding to the input value. An example of an encoder is the octal-to-binary encoder, whose truth table is given in the following Table. It has eight inputs, one for each of the octal digits, and three outputs that generate the corresponding binary number. It is assumed that only one input has a value of 1 at any given time; otherwise, the circuit has no meaning.

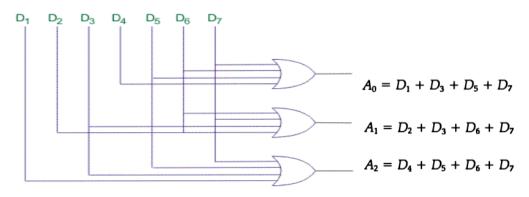

The encoder can be implemented with OR gates whose inputs are determined directly from the truth table. Output  $A_0 = 1$  if the input octal digit is 1 or 3 or 5 or 7. Similar conditions apply for the other two outputs. These conditions can be expressed by the following Boolean functions:

$A_0 = D_1 + D_3 + D_5 + D_7$  $A_1 = D_2 + D_3 + D_6 + D_7$  $A_2 = D_4 + D_5 + D_6 + D_7$

The encoder can be implemented with three OR gates.

|    |                |    | Inp   | uts   |    |       |    |                | Output | S |

|----|----------------|----|-------|-------|----|-------|----|----------------|--------|---|

| D7 | D <sub>6</sub> | D₅ | $D_4$ | $D_3$ | D₂ | $D_1$ | Do | A <sub>2</sub> | Aı     | A |

| 0  | 0              | 0  | 0     | 0     | 0  | 0     | 1  | 0              | 0      | 0 |

| 0  | 0              | 0  | 0     | 0     | 0  | 1     | 0  | 0              | 0      | 1 |

| 0  | 0              | 0  | 0     | 0     | 1  | 0     | 0  | 0              | 1      | 0 |

| 0  | 0              | 0  | 0     | 1     | 0  | 0     | 0  | 0              | 1      | 1 |

| 0  | 0              | 0  | 1     | 0     | 0  | 0     | 0  | 1              | 0      | 0 |

| 0  | 0              | 1  | 0     | 0     | 0  | 0     | 0  | 1              | 0      | 1 |

| 0  | 1              | 0  | 0     | 0     | 0  | 0     | 0  | 1              | 1      | 0 |

| 1  | 0              | 0  | 0     | 0     | 0  | 0     | 0  | 1              | 1      | 1 |

### COMPUTER ORGANIZATION AND ARCHITECTURE

### 1.10 Multiplexers

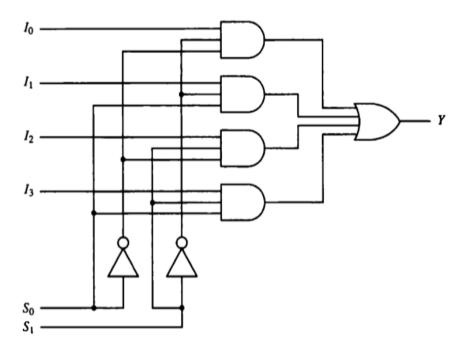

A multiplexer is a combinational circuit that receives binary information from one of  $2^n$  input data lines and directs it to a single output line. The selection of a particular input data line for the output is determined by a set of selection inputs. A  $2^n$ -to-1 multiplexer has  $2^n$  input data lines and n input selection lines whose bit combinations determine which input data are selected for the output. A4-to-1-line multiplexer is shown in the following Figure. Each of the four data inputs I<sub>0</sub> through I<sub>1</sub> is applied to one input of an AND gate.

The two selection inputs  $S_1$  and  $S_0$  are decoded to select a particular AND gate. The outputs of the AND gates are applied to a single OR gate to provide the single output. To demonstrate the circuit operation, consider the case when  $S_1S_0 = 10$ . The AND gate associated with input I<sub>1</sub> has two of its inputs equal to 1. The third input of the gate is connected to I<sub>2</sub>. The other three AND gates have at least one input equal to 0, which makes their outputs equal to 0. The OR gate output is now equal to the value of I<sub>2</sub>, thus providing a path from the selected input to the output.

The 4-to-1 line multiplexer of Figure has six inputs and one output. A truth table describing the circuit needs 64 rows since six input variables can have  $2^6$  binary combinations. A more convenient way to describe the operation of multiplexers is by means of a function table. The function table for the multiplexer is shown in the following Table. The table demonstrates the relationship between the four data inputs and the single output as a function of the selection inputs  $S_1$  and  $S_0$ .When the selection inputs are equal to 00, output Y is equal to input  $I_0$ . When the selection inputs are equal to 01, input11 has a path to output Y, and similarly for the other two combinations. The multiplexer is also called a data selector, since it selects one of many data inputs and steers the binary information to the output.

COMPUTER ORGANIZATION AND ARCHITECTURE

| Function | Table | for 4-to- | l-Line | Multiplexer |

|----------|-------|-----------|--------|-------------|

|----------|-------|-----------|--------|-------------|

| Sel            | lect | Output         |

|----------------|------|----------------|

| S <sub>1</sub> | So   | Ŷ              |

| 0              | 0    | Io             |

| 0              | 1    | $I_1$          |

| 1              | 0    | $I_2$          |

| 1              | 1    | I <sub>3</sub> |

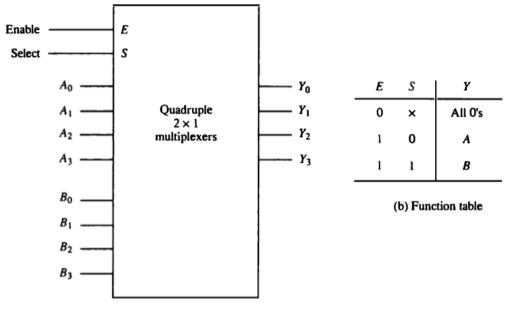

The AND gates and inverters in the multiplexer resemble a decoder circuit, and indeed they decode the input selection lines. In general, a 2"-to-1line multiplexer is constructed from an n-to-2" decoder by adding to it 2" input lines, one from each data input. The size of the multiplexer is specified by the number 2" of its data inputs and the single output. It is then implied that it also contains n input selection lines. The multiplexer is often abbreviated as MUX. As in decoders, multiplexers may have an enable input to control the operation of the unit. When the enable input is in the inactive state, the outputs are disabled, and when it is in the active state, the circuit functions as a normal multiplexer. The enable input is useful for expanding two or more multiplexers to a multiplexer with a larger number of inputs. In some cases two or more multiplexers are enclosed within a single integrated circuit package. The selection and the enable inputs in multiple-unit construction are usually common to all multiplexers.

### COMPUTER ORGANIZATION AND ARCHITECTURE

(a) Block diagram

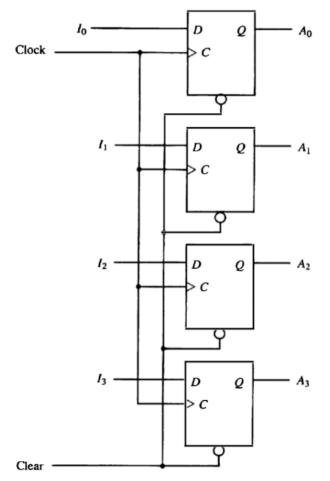

#### 1.11 Registers

A register is a group of flip-flops with each flip-flop capable of storing one bit of information. An n-bit register has a group of n flip-flops and is capable of storing any binary information of n bits. In addition to the flip-flops, a register may have combinational gates that perform certain data-processing tasks. In its broadest definition, a register consists of a group of flip-flops and gates that effect their transition. The flip-flops hold the binary information and the gates control when and how new information is transferred into the register.

The simplest register is one that consists only of flip-flops, with no external gates. The following figure shows such a register constructed with four D flip-flops. The common clock input triggers all flip-flops on the rising edge of each pulse, and the binary data available at the four inputs are transferred into the 4-bit register. The four outputs can be sampled at any time to obtain the binary information stored in the register. The clear input goes to a special terminal in each flip-flop. When this input goes to 0, all flip-flops are reset asynchronously. The clear input is useful for clearing the register to all 0's prior to its clocked operation. The clear input must be maintained at logic 1 during normal clocked operation. Note that the clock signal enables the D input but that the clear input is independent of the clock. The transfer of new information into a register is referred to as loading the register.

COMPUTER ORGANIZATION AND ARCHITECTURE

If all the bits of the register are loaded simultaneously with a commonclock pulse transition, we say that the loading is done in parallel. A clock transition applied to the C inputs of the register of Figure will load all four inputs  $I_0$  through  $I_3$  in parallel. In this configuration, the clock must be inhibited from the circuit if the content of the register must be left unchanged.

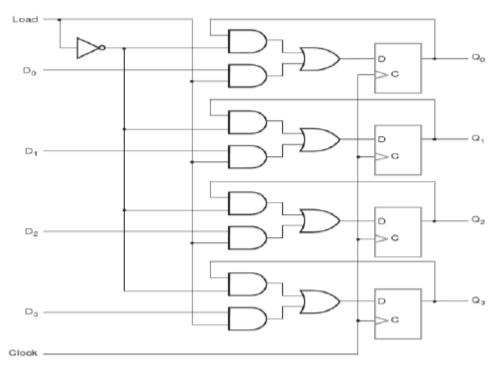

### 1.11.1 Register with Parallel Load

Most digital systems have a master clock generator that supplies a continuous train of clock pulses. The clock pulses are applied to all flip-flops and registers in the system. The master clock acts like a pump that supplies a constant beat to all parts of the system. A separate control signal must be used to decide which specific clock pulse will have an effect on a particular register. A 4-bit register with a load control input that is directed through gates and into the D inputs is shown in the folowing Figure.

The C inputs receive clock pulses at all times. The buffer gate in the dock input reduces the power requirement. With each clock pulse, the D input determines the next state of the output. To leave the output unchanged, it is necessary to make the D input equal to the present value of the output. Note that the clock pulses are applied to the C inputs at all times. The load input determines whether the next pulse will accept new information or leave the information in the register intact.

COMPUTER ORGANIZATION AND ARCHITECTURE

The transfer of information from the inputs into the register is done simultaneously with all four bits during a single pulse transition.

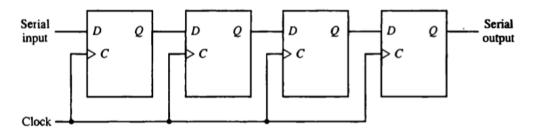

### 1.11.2 Shift Registers

A register capable of shifting its binary information in one or both directions is called a shift register. The logical configuration of a shift register consists of a chain of flip-flops in cascade, with the output of one flip-flop connected to the input of the next flip-flop. All flip-flops receive common clock pulses that initiate the shift from one stage to the next. The simplest possible shift register is one that uses only flip-flops, as shown in Figure. The output of a given flip-flop is connected to the D input of the flip-flop at its right. The clock is common to all flip-flops. The serial input determines what goes into the leftmost position during the shift. The serial output is taken from the output of the rightmost flip-flop. Sometimes it is necessary to control the shift so that it occurs with certain clock pulses but not with others. This can be done by inhibiting the clock from the input of the register if we do not want it to shift.

### COMPUTER ORGANIZATION AND ARCHITECTURE

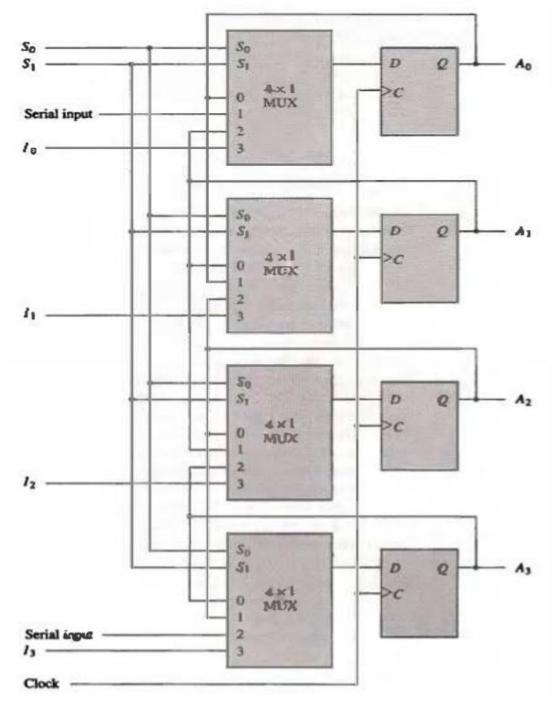

### 1.11.3 Bidirectional Shift Register with Parallel Load

A register capable of shifting in one direction only is called a unidirectional shift register. A register that can shift in both directions is called a bidirectional shift register. The most general shift register has all the capabilities listed below. Others may have some of these capabilities, with at least one shift operation.

1. An input for clock pulses to synchronize all operations.

2. A shift-right operation and a serial input line associated with the shiftright.

3. A shift-left operation and a serial input line associated with the shift-left.

4. A parallel load operation and n input lines associated with the parallel transfer.

5. n parallel output lines.

6. A control state that leaves the information in the register unchanged even though clock pulses are applied continuously.

A 4-bit bidirectional shift register with parallel load is shown in the following Figure. Each stage consists of a D flip-flop and a 4 x 1 multiplexer. The two selection inputs  $S_1$  and  $S_0$  select one of the multiplexer data inputs for the D flip-flop. The selection lines control the mode of operation of the register according to the function table shown in the following Table. When the mode control  $S_1S_0 = 00$ , data input 0 of each multiplexer is selected. This condition forms a path from the output of each flip-flop into the input of the same flip-flop. The next clock transition transfers into each flip-flop the binary value it held previously, and no change of state occurs.

When  $S_1S_0 = 01$ , the terminal marked 1 in each multiplexer has a path to the D input of the corresponding flip-flop. This causes a shift-right operation, with the serial input data transferred into flip-flop  $A_0$  and the content of each flip-flop  $A_{i-1}$  transferred into flip-flop  $A_i$  for i = 1, 2, 3. When  $S_1S_0 = 10$  a shift-left operation results, with the other serial input data going into flip-flop A, and the content of flip-flop  $A_{i+1}$  transferred into flip-flop  $A_i$  for i = 0, 1, 2. When  $S_1S_0 = 11$ , the binary information from each input  $I_0$  through  $I_3$  is transferred into the corresponding flip-flop, resulting in a parallel load operation. Note that the way the diagram is drawn, the shift-right operation shifts the contents of the register in the down direction while the shift left operation causes the contents of the register to shift in the upward direction.

| Mode control |    |                    |

|--------------|----|--------------------|

| S1           | So | Register operation |

| 0            | 0  | No change          |

| 0            | 1  | Shift right (down) |

| 1            | 0  | Shift left (up)    |

| 1            | 1  | Parallel load      |

### COMPUTER ORGANIZATION AND ARCHITECTURE

Shift registers are often used to interface digital systems situated remotely from each other. For example, suppose that it is necessary to transmit ann-bit quantity between two points. If the distance between the source and the destination is too far, it will be expensive to use n lines to transmit the n bits in parallel. It may be more economical to use a single line and transmit the information serially one bit at a time. The transmitter loads the n-bit data inparallel into a shift register and then transmits the data from the serial output line. The receiver accepts the data serially

### COMPUTER ORGANIZATION AND ARCHITECTURE

into a shift register through its serial input line. When the entire n bits are accumulated, they can be taken from the outputs of the register in parallel. Thus, the transmitter performs a parallel-toserial conversion of data and the receiver converts the incoming serial data back to parallel data transfer.

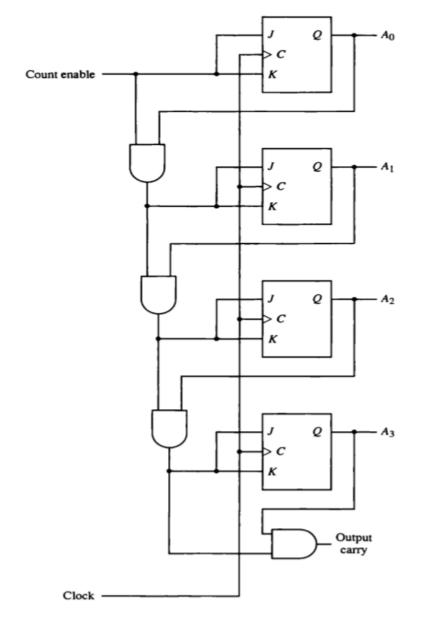

### **1.12 Binary Counters**

A register that goes through a predetermined sequence of states upon the application of input pulses is called a counter. The input pulses may be clock pulses or may originate from an external source. They may occur at uniform intervals of time or at random. Counters are found in almost all equipment containing digital logic. They are used for counting the number of occurrences of an event and are useful for generating timing signals to control the sequence of operations in digital computers. Of the various sequences a counter may follow, the straight binary sequence is the simplest and most straightforward. A counter that follows the binary number sequence is called a binary counter. An n-bit binary counter is a register of n flip-flops and associated gates that follows a sequence of states according to the binary count of n bits, from 0 to  $2^n - 1$ .

Going through a sequence of binary numbers such as 0000, 0001, 0010, 0011, and so on, we note that the lower-order bit is complemented after every count and every other bit is complemented from one count to the next if and only if all its lower-order bits are equal to 1. For example, the binary count from 0111 (7) to 1000 (8) is obtained by

- (a) complementing the low-order bit,

- (b) complementing the second-order bit because the first bit of 0111 is 1,

- (c) complementing the third-order bit because the first two bits of 0111 are 1's, and

- (d) complementing the fourth-order bit because the first three bits of 0111 are all1's.

Synchronous binary counters have a regular pattern, as can be seen from the 4-bit binary counter shown in Figure. The C inputs of all flip-flops receive the common clock. If the count enable is 0, all J and K inputs are maintainedat 0 and the output of the counter does not change. The first stage  $A_0$  is complemented when the counter is enabled and the clock goes through a positive transition. Each of the other three flip-flops are complemented when all previous least significant flip-flops are equal to 1 and the count is enabled. The chain of AND gates generate the required logic for the J and K inputs. Theoutput carry can be used to extend the counter to more stages, with each stage having an additional flip-flop and an AND gate.

### **COMPUTER ORGANIZATION AND ARCHITECTURE**

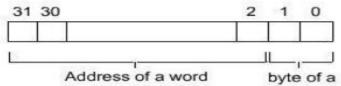

### 1.13 Memory Unit

A memory unit is a collection of storage cells together with associated circuits needed to transfer information in and out of storage. The memory stores binary information in groups of bits called words. A word in memory is an entity ofbits that move in and out of storage as a unit. A memory word is a group of I's and 0's and may represent a number, an instruction code, one or more alphanumeric characters, or any other binary-coded information. A group of eight bits is called a byte. Most computer memories use words whose number of bits is a multiple of 8. Thus a 16-bit word contains two bytes, and a 32-bit word is made up of four bytes. The capacity of memories in commercial computers is usually stated as the total number of bytes that can be stored.

COMPUTER ORGANIZATION AND ARCHITECTURE

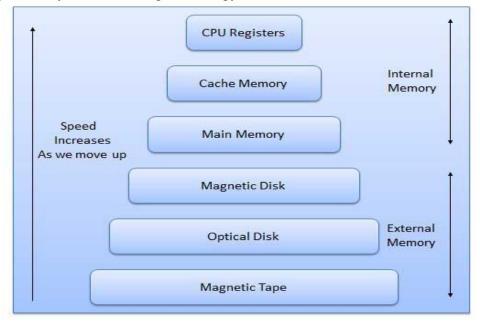

Two major types of memories are used in computer systems: randomaccess memory (RAM) and read-only memory (ROM).

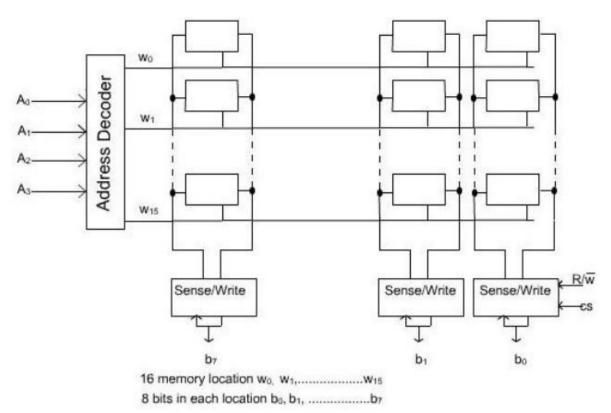

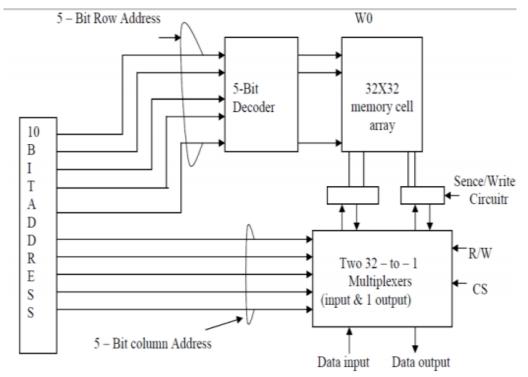

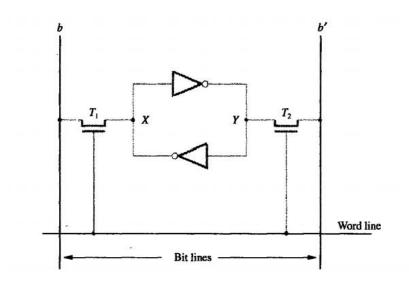

### 1.13.1 Random-Access Memory

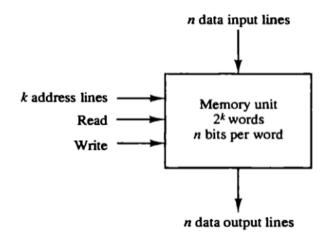

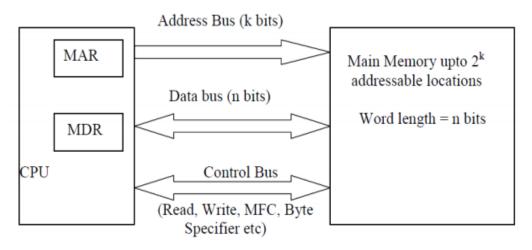

In random-access memory (RAM) the memory cells can be accessed for information transfer from any desired random location. That is, the process of locating a word in memory is the same and requires an equal amount of time no matter where the cells are located physically in memory: thus the name "random access." Communication between a memory and its environment is achieved through data input and output lines, address selection lines, and control lines that specify the direction of transfer. A block diagram of a RAM unit is shown in the following figure. The n data input lines provide the information to be stored in memory, and the n data output lines supply the information coming out of memory. The k address lines provide a binary number of k bits that specify a particular word chosen among the 2' available inside the memory. The two control inputs specify the direction of transfer desired. The two operations that a random-access memory can perform are the write and read operations. The write signal specifies a transfer-in operation and the read signal specifies a transfer-out operation. On accepting one of these control signals, the internal circuits inside the memory provide the desired function.

The steps that must be taken for the purpose of transferring a new word to be stored into memory are as follows:

- 1. Apply the binary address of the desired word into the address lines.

- 2. Apply the data bits that must be stored in memory into the data input lines.

- 3. Activate the write input.

The memory unit will then take the bits presently available in the input data lines and store them in the word specified by the address lines. The steps that must be taken for the purpose of transferring a stored word out of memory are as follows:

- 1. Apply the binary address of the desired word into the address lines.

- 2. Activate the read input.

### COMPUTER ORGANIZATION AND ARCHITECTURE

The memory unit will then take the bits from the word that has been selected by the address and apply them into the output data lines. The content of the selected word does not change after reading.

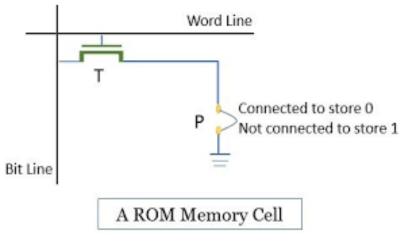

### 1.13.2 Read-Only Memory

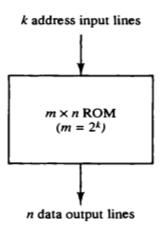

As the name implies, a read-only memory (ROM) is a memory unit that performs the read operation only; it does not have a write capability. This implies that the binary information stored in a ROM is made permanent during the hardware production of the unit and cannot be altered by writing different words into it. Whereas a RAM is a general-purpose device whose contents can be altered during the computational process, a ROM is restricted to reading words that are permanently stored within the unit. The binary information to be stored, specified by the designer, is then embedded in the unit to form the required interconnection pattern. ROMs come with special internal electronic fuses that can be "programmed" for a specific configuration. Once the pattern is established, it stays within the unit even when power is turned off and on again.

ROMs find a wide range of applications in the design of digital systems. Basically, a ROM generates an input---output relation specified by a truth table. As such, it can implement any combinational circuit with k inputs and n outputs. When employed in a computer system as a memory unit, the ROM is used for storing fixed programs that are not to be altered and for tables of constants that are not subject to change. ROM is also employed in the design of control units for digital computers. As such, they are used to store coded information that represents the sequence of internal control variables needed for enabling the various operations in the computer. A control unit that utilizes a ROM to store binary control information is called a microprogrammed control unit.

### **1.13.3** Types of ROMs

The required paths in a ROM may be programmed in three different ways.

1. <u>Mask programming</u>, is done by the semiconductor company during the last fabrication process of the unit. The procedure for fabricating a ROM requires that the customer fill out the truth table that he or she wishes the ROM to satisfy. The truth table may be submitted in a special form provided by the manufacturer or in a specified format on a computer output medium. The manufacturer makes the corresponding mask for the paths to produce the l's and O's according to

### COMPUTER ORGANIZATION AND ARCHITECTURE

the customer's truth table. This procedure is costly because the vendor charges the customer a special fee for custom masking the particular ROM. For this reason, mask programming is economical only if a large quantity of the same ROM configuration is to be ordered.

- 2. **Programmable read-only memory**: For small quantities it is more economical to use a second type of ROM called a **programmable read-only memory** or PROM. When ordered. PROM units contain all the fuses intact, giving all 1's in the bits of the stored words. The fuses in the PROM are blown by application of current pulses through the output terminals for each address. A blown fuse defines a binary 0 state, and an intact fuse gives a binary 1 state. This allows users to program PROMs in their own laboratories to achieve the desired relationship between input addresses and stored words. Special instruments called PROM programmers are available commercially to facilitate this procedure. In any case, all procedures for programming ROMs are hardware procedures even though the word "programming" is used. The hardware procedure for programming ROMs or PROMs is irreversible, and once programmed, the fixed pattern is permanent and cannot be altered. Once a bit pattern has been established, the unit must be discarded if the bit pattern is to be changed.

- 3. <u>Erasable PROM or EPROM</u>. : A third type of ROM available is called **erasable PROM** or EPROM. The EPROM can be restructured to the initial value even though its fuses have been blown previously. When the EPROM is placed under a special ultraviolet light for a given period of time, the shortwave radiation discharges the internal gates that serve as fuses. After erasure, the EPROM returns to its initial state and can be reprogrammed to a new set of words. Certain PROMs can be erased with electrical signals instead of ultraviolet light. These PROMs are called **electrically erasable PROM** or EEPROM.

### COMPUTER ORGANIZATION AND ARCHITECTURE

# <u>UNIT-2</u>

# **Data Representation, Basic Computer Organization**

### **Data Types**

The data types found in the registers of digital computers may be classified as being one of the following categories:

(1) Numbers used in arithmetic computations,

(2) Letters of the alphabet used in data processing. and

(3) Other discrete symbols used for specific purposes.

All types of data, except binary numbers, are represented in computer registers in binary coded form. This is because registers are made up of flip-flops and flip-flops are two-state devises that can store only l's and 0's. The binary number system is the most natural system to use in a digital computer. But sometimes it is convenient to employ different number systems, especially the decimal number system, since it is used by people to perform arithmetic computations.

### **Number Systems**

A number system of base, or radix, r is a system that uses distinct symbols for r digits. Numbers are represented by a string of digit symbols. To determine the quantity that the number represents, it is necessary to multiply each digit by an integer power of r and then form the sum of all weighted digits. For example, the decimal number system in everyday use employs the radix 10 system. The 10 symbols are 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. The string of digits 724.5 is interpreted to represent the quantity

$$7 \times 10^{2} + 2 \times 10^{1} + 4 \times 10^{0} + 5 \times 10^{-1}$$

that is, 7 hundreds, plus 2 tens, plus 4 units, plus 5 tenths. Every decimal number can be similarly interpreted to find the quantity it represents. The binary number system uses the radix 2. The two digit symbols used are 0 and 1. The string of digits 101101 is interpreted to represent the quantity

$$x2^{5}+0x2^{4}+1x2^{3}+1x2^{2}+0x2^{1}+1x2^{0}=45$$

To distinguish between different radix numbers, the digits will be enclosed in parentheses and the radix of the number inserted as a subscript. For example, to show the equality between decimal and binary forty-five we will write  $(101101)_2 = (45)_{10}$ .

Besides the decimal and binary number systems, the octal (radix 8) and hexadecimal (radix 16) are important in digital computer work. The eight symbols of the octal system are 0, 1, 2, 3, 4, 5, 6, and 7. The 16 symbols of the hexadecimal system are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F. The last six symbols are, unfortunately, identical to the letters of the alphabet and can cause confusion at times. However, this is the convention that has been adopted. When used to represent hexadecimal digits, the symbols A, B, C, D, E, F correspond to the decimal numbers 10, 11, 12, 13, 14, 15, respectively. A number in radix r can be converted to the familiar decimal system by forming the sum of the weighted digits. For example, octal 736.4 is converted to decimal as follows:

$(736.4)_8 = 7 X 8^2 + 3 X 8^1 + 6 X 8^0 + 4 X 8^{-1} = 7 X 64 + 3 X 8 + 6 X 1 + 4/8 = (478.5)_{10}$

### COMPUTER ORGANIZATION AND ARCHITECTURE

The equivalent decimal number of hexadecimal F3 is obtained from the following calculation:

$(F3)_{16} = F X 16 + 3 = 15 X 16 + 3 = (243)_{10}$

### **Octal and Hexadecimal Numbers**

The conversion from Decimal to Binary, Octal, and Hexadecimal representation plays an important part in digital computers. Since  $2^3 = 8$  and  $2^4 = 16$ , each octal digit corresponds to three binary digits and each hexadecimal digit corresponds to four binary digits. The conversion from binary to octal is easily accomplished by partitioning the binary number into groups of three bits each. The corresponding octal digit is then assigned to each group of bits and the string of digits so obtained gives the octal equivalent of the binary number. Consider, for example, a 16-bit register.

| Integer = 41                       |                      | <b>Fraction = 0.6875</b>     |  |

|------------------------------------|----------------------|------------------------------|--|

| 41                                 |                      | 0.6875                       |  |

| 20                                 | 1                    | 2                            |  |

| 10                                 | 0                    | 1.3750                       |  |

| 5                                  | 0                    | x 2                          |  |

| 2                                  | 1                    | 0.7500                       |  |

| 5<br>2<br>1<br>0                   | 0                    | x 2                          |  |

| 0                                  | 1                    | 1.5000                       |  |

|                                    |                      | x 2                          |  |

|                                    |                      | 1.0000                       |  |

| (41)                               | $_{10} = (101001)_2$ | $(0.6875)_{10} = (0.1011)_2$ |  |

| $(41.6875)_{10} = (101001.1011)_2$ |                      |                              |  |

Conversion of decimal 41.6875 into binary.

| 1 2  | 7    | 5 4  | 3    | Octal       |

|------|------|------|------|-------------|

| 1010 | 1111 | 0110 | 0011 | Binary      |

| A    | F    | 6    | 3    | Hexadecimal |

Binary, octal, and hexadecimal conversion

COMPUTER ORGANIZATION AND ARCHITECTURE

|         | Decimal equivalent | Binary-coded octal | Octal<br>number |

|---------|--------------------|--------------------|-----------------|

| 1       | 0                  | 000                | 0               |

|         | 1                  | 001                | 1               |

| Code    | 2                  | 010                | 2               |

| for one | 3                  | 011                | 3               |

| octal   | 4                  | 100                | 4               |

| digit   | 5                  | 101                | 5               |

| I       | 6                  | 110                | 6               |

| Ļ       | 7                  | 111                | 7               |

|         | 8                  | 001 000            | 10              |

|         | 9                  | 001 001            | 11              |

|         | 10                 | 001 010            | 12              |

|         | 20                 | 010 100            | 24              |

|         | 50                 | 110 010            | 62              |

|         | 99                 | 001 100 011        | 143             |

|         | 248                | 011 111 000        | 370             |

### TABLE 3-1 Binary-Coded Octal Numbers

### **COMPUTER ORGANIZATION AND ARCHITECTURE**

| Hexadecimal<br>number | Binary-coded<br>hexadecimal | Decimal equivalent |             |

|-----------------------|-----------------------------|--------------------|-------------|

| 0                     | 0000                        | 0                  | Î           |

| 1                     | 0001                        | 1                  |             |

| 2                     | 0010                        | 2                  | 1           |

| 3                     | 0011                        | 3                  |             |

| 4                     | 0100                        | 4                  |             |

| 5                     | 0101                        | 5                  |             |

| 6                     | 0110                        | 6                  | Code        |

| 7                     | 0111                        | 7                  | for one     |

| 8                     | 1000                        | 8                  | hexadecimal |

| 9                     | 1001                        | 9                  | digit       |

| Α                     | 1010                        | 10                 | ¢.          |

| в                     | 1011                        | 11                 | 1           |

| С                     | 1100                        | 12                 |             |

| D                     | 1101                        | 13                 |             |

| E                     | 1110                        | 14                 |             |

| F                     | 1111                        | 15                 | Ļ           |

| 14                    | 0001 0100                   | 20                 |             |

| 32                    | 0011 0010                   | 50                 |             |

| 63                    | 0110 0011                   | 99                 |             |

| F8                    | 1111 1000                   | 248                |             |

#### TABLE 3-2 Binary-Coded Hexadecimal Numbers

### **Decimal Representation**

Binary Number System is the most natural system for a computer, but the people are accustomed to the decimal system. One way to solve this conflict is to convert all input decimal numbers into binary numbers, let the computer perform all the operations in binary and convert the result into decimal. It is also possible for the computer to perform all arithmetic operations directly with decimal numbers provided they are placed in the registers in a coded form.

It is important to understand the difference between the conversion of decimal numbers into binary and the binary coding of decimal numbers. For example when converted into binary number, the decimal number 99 is represented as 1100011. But when represented in BCD it is

#### 1001 1001

Few decimal numbers and their representation in BCD are as follows

## **COMPUTER ORGANIZATION AND ARCHITECTURE**

|         | Binary-coded decimal<br>(BCD) number | Decimal<br>number |

|---------|--------------------------------------|-------------------|

| t       | 0000                                 | 0                 |

|         | 0001                                 | 1                 |

|         | 0010                                 | 2                 |

| Code    | 0011                                 | 3                 |

| for one | 0100                                 | 4                 |

| decimal | 0101                                 | 5                 |

| digit   | 0110                                 | 6                 |

|         | 0111                                 | 7                 |

|         | 1000                                 | 8                 |

| Ļ       | 1001                                 | 9                 |

|         | 0001 0000                            | 10                |

|         | 0010 0000                            | 20                |

|         | 0101 0000                            | 50                |

|         | 1001 1001                            | 99                |

|         | 0010 0100 1000                       | 248               |

TABLE 3-3 Binary-Coded Decimal (BCD) Numbers

### **Alphanumeric Representation**

Many applications of digital computers require handling of data that consists of not only of numbers but also letters and special characters. The standard alphanumeric binary code is ASCII (American Standard Code for Information Interchange) which uses 7 bits to code 128 characters.

### **COMPUTER ORGANIZATION AND ARCHITECTURE**

| Character | Binary<br>code | Character | Binary<br>code |

|-----------|----------------|-----------|----------------|

| А         | 100 0001       | 0         | 011 0000       |

| в         | 100 0010       | 1         | 011 0001       |

| С         | 100 0011       | 2         | 011 0010       |

| D         | 100 0100       | 3         | 011 0011       |

| E         | 100 0101       | 4         | 011 0100       |

| F         | 100 0110       | 5         | 011 0101       |

| G         | 100 0111       | 6         | 011 0110       |

| н         | 100 1000       | 7         | 011 0111       |

| I         | 100 1001       | 8         | 011 1000       |

| J         | 100 1010       | 9         | 011 1001       |

| ĸ         | 100 1011       |           |                |

| L         | 100 1100       |           |                |

| M         | 100 1101       | space     | 010 0000       |

| N         | 100 1110       |           | 010 1110       |

| 0         | 100 1111       | (         | 010 1000       |

| Р         | 101 0000       | +         | 010 1011       |

| Q         | 101 0001       | \$        | 010 0100       |

| R         | 101 0010       | •         | 010 1010       |

| S         | 101 0011       | )         | 010 1001       |

| Т         | 101 0100       | -         | 010 1101       |

| U         | 101 0101       | /         | 010 1111       |

| v         | 101 0110       | ,         | 010 1100       |

| w         | 101 0111       | =         | 011 1101       |

| x         | 101 1000       |           |                |

| Y         | 101 1001       |           |                |

| Z         | 101 1010       |           |                |

TABLE 3-4 American Standard Code for Information Interchange (ASCII)

### Complements

Complements are used in digital computers for simplifying the subtraction operation and for logical manipulation. There are two types of complements for each base r system: the r's complement and the (r - 1)'s complement.

9' s complement ,10's complement

l's complement ,2's complement

When the value of the base r is substituted in the name, the two types are referred to as the 2's and 1's complement for binary numbers and the 10's and 9's complement for decimal numbers.

### (r - l)'s Complement

Given a number N in base r having n digits, the (r - 1)'s complement of N is defined as

### **COMPUTER ORGANIZATION AND ARCHITECTURE**

(r' - 1) - N.

For decimal numbers r = 10 and r - 1 = 9, so the 9's complement of N is

(10' - 1) - N.

Now, 10' represents a number that consists of a single 1 followed by n 0's. 10' - 1 is a number represented by n 9's.

For example, with n = 4 we have  $10^4 = 10000$  and  $10^4 - 1 = 9999$ . It follows that the 9' s complement of a decimal number is obtained by subtracting each digit from 9.

For example, the 9's complement of 546700 is

999999 - 546700 = 453299

and the 9's complement of I2389 is 99999 - 12389 = 876I0.

For binary numbers, r = 2 and r - 1 = 1, so the 1's complement of N is

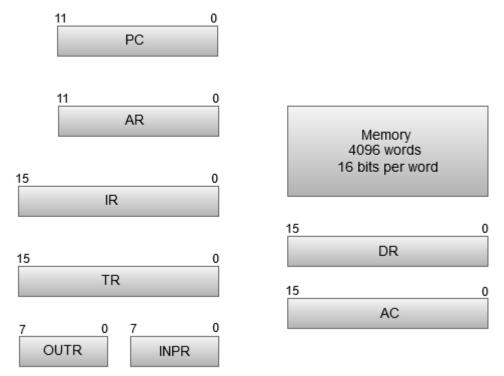

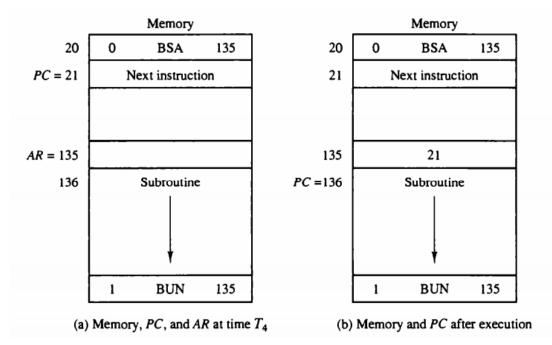

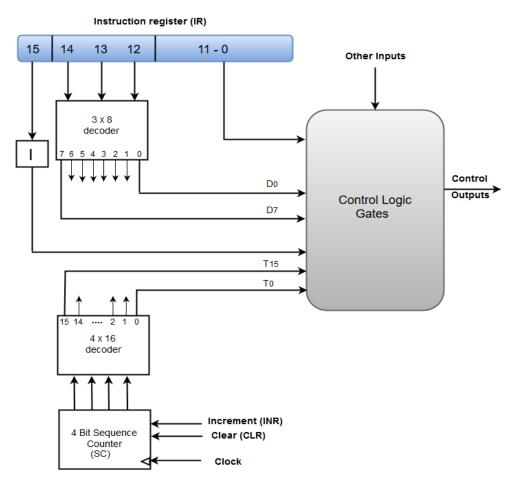

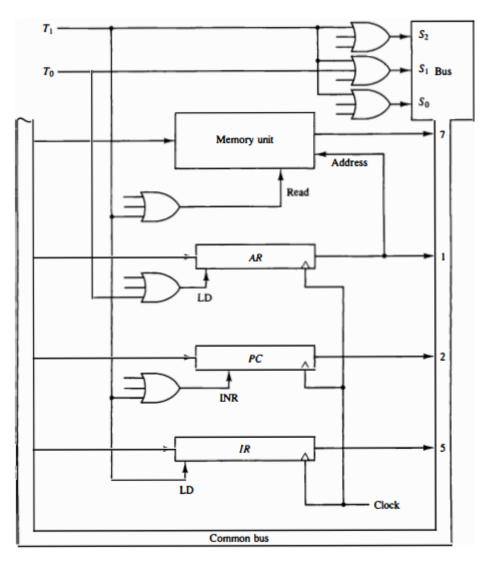

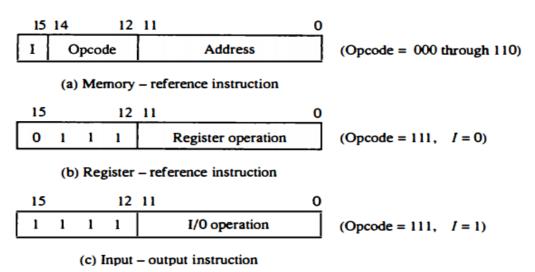

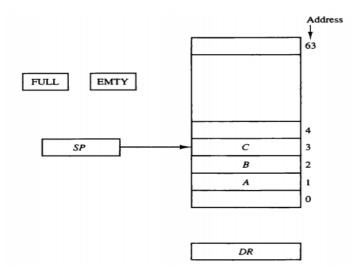

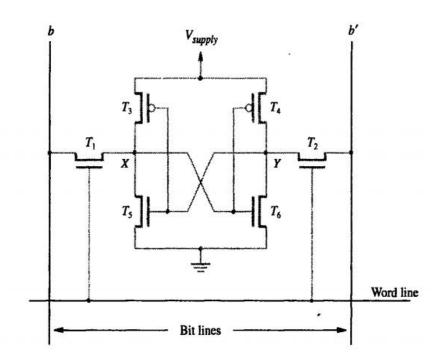

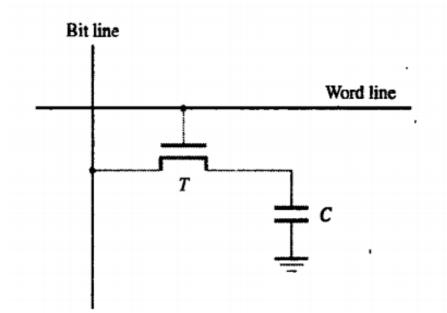

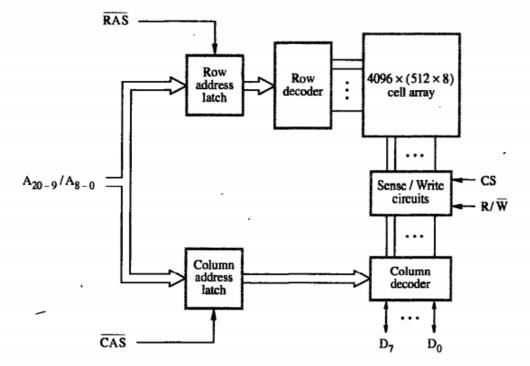

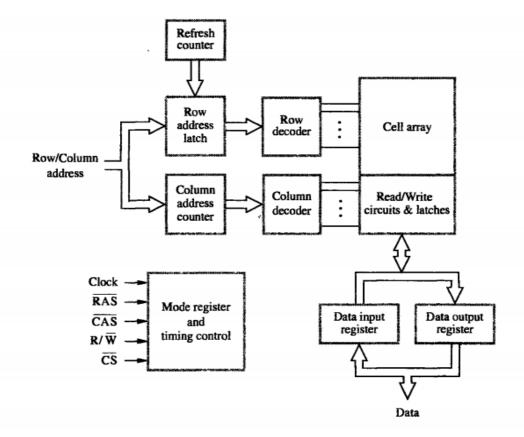

(2' - 1) - N.